AI Agents Develop Verilog Simulator, 580K Lines in 43 Days

Sonic Intelligence

AI agents rapidly built a comprehensive open-source Verilog simulator.

Explain Like I'm Five

"Imagine you need to build a very complicated Lego castle, but instead of you doing every single step, you have a super-smart robot helper that knows all the rules. In just 43 days, this robot built a huge, working Lego castle (a Verilog simulator) that usually costs a lot of money and takes a long time for humans to build. It helps engineers check if their computer chips will work correctly."

Deep Intelligence Analysis

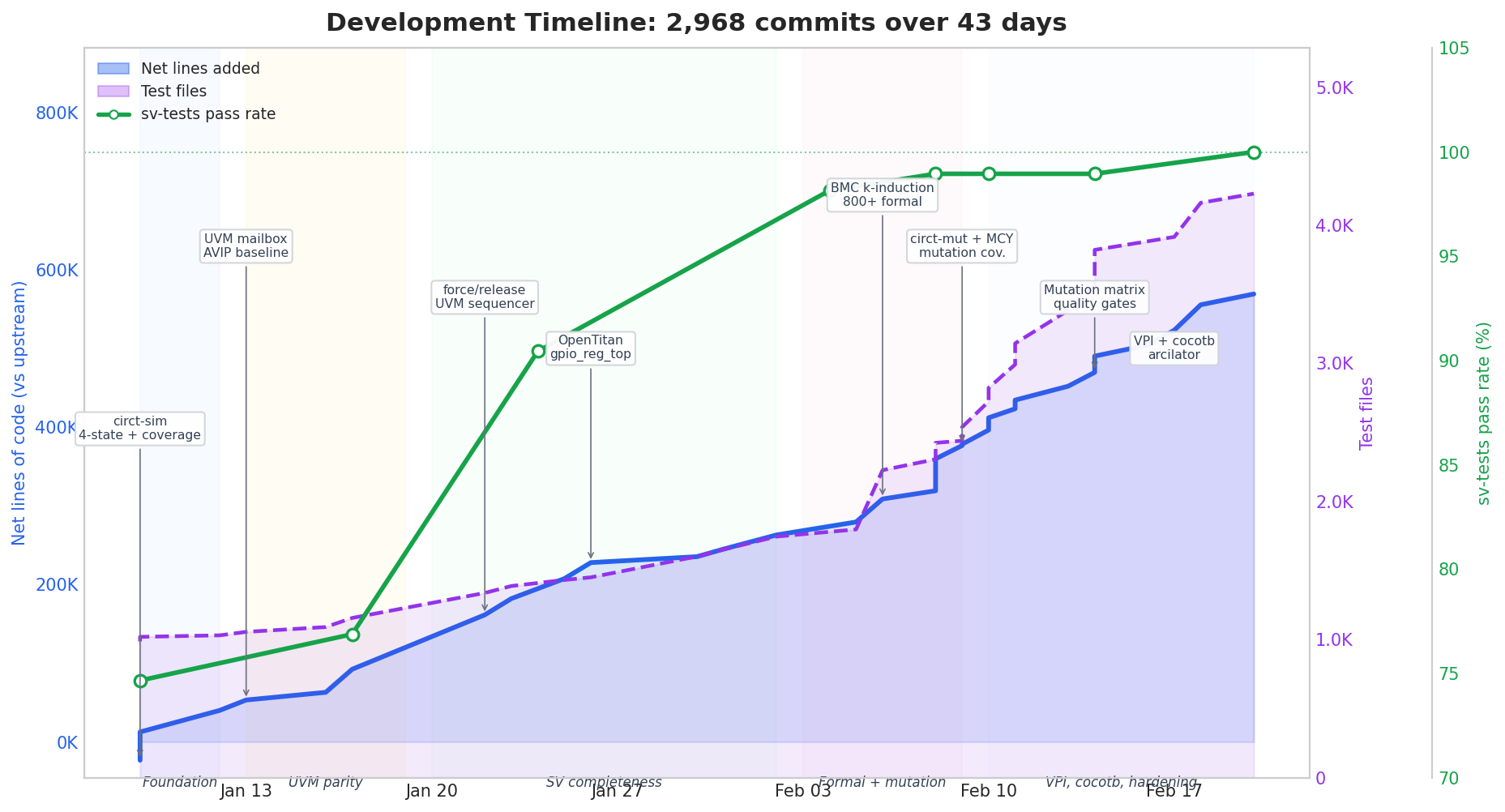

The AI agents successfully implemented a full event-driven simulator, integrated VPI/cocotb, added UVM runtime support, and incorporated advanced verification techniques such as bounded model checking, logic equivalence checking, and mutation testing. This resulted in a practical, end-to-end open-source verification stack capable of simulating real-world protocol testbenches. The project's rapid pace is evidenced by commit velocities peaking at 124 commits per day in week seven, and a 4.3x increase in test files, growing from 987 to 4,229.

A key driver for progress was the sv-tests suite from the CHIPS Alliance, which measures compliance with the SystemVerilog standard. The project aims to achieve 100% IEEE support, a significant improvement over existing free simulators like Verilator (94%) and Icarus (80%). The distribution of work highlights the AI's focus, with formal verification (bounded model checking and logic equivalence checking) and mutation testing accounting for over 1,000 commits, representing 34% of the total. This demonstrates AI agents' proficiency in handling well-specified, high-volume engineering tasks, offering a potential cost-effective alternative to expensive commercial Electronic Design Automation (EDA) toolchains and democratizing access to sophisticated hardware verification capabilities. The project serves as a compelling case study for the application of agentic AI in complex engineering domains.

[EU AI Act Art. 50 Compliant: This analysis was generated by an AI model, Gemini 2.5 Flash, based on the provided source material. No external data or prior knowledge was used.]

Impact Assessment

This demonstrates AI agents' capability to tackle complex, labor-intensive engineering problems in hardware design, potentially democratizing access to advanced verification tools and significantly reducing development costs in the EDA industry.

Key Details

- AI agents generated 580,430 lines of code across 3,846 files in 43 days.

- Achieved 2,968 commits on a CIRCT fork during January-February 2026.

- Added event-driven simulation, VPI/cocotb, UVM runtime, bounded model checking, logic equivalence checking, and mutation testing.

- Increased test files from 987 to 4,229 (4.3x increase).

- Project aims for 100% IEEE SystemVerilog support, surpassing existing free simulators (Verilator 94%, Icarus 80%).

- Formal verification and mutation testing accounted for over 1,000 commits (34% of total).

Optimistic Outlook

The rapid development of a robust, open-source Verilog simulator using AI agents signals a paradigm shift in hardware design and verification. This could drastically lower the barrier to entry for smaller teams and startups, fostering innovation by providing cost-effective alternatives to expensive commercial EDA tools and accelerating the development cycle for complex hardware.

Pessimistic Outlook

While impressive, the reliance on AI agents for such a critical infrastructure raises questions about long-term maintainability, potential for subtle bugs introduced by AI, and the need for extensive human oversight. The "volume" nature of the work might mask deeper design flaws, and achieving full industry acceptance for AI-generated verification stacks could face significant hurdles.

Get the next signal in your inbox.

One concise weekly briefing with direct source links, fast analysis, and no inbox clutter.

More reporting around this signal.

Related coverage selected to keep the thread going without dropping you into another card wall.